In the rapidly evolving landscape of technology, the constant demand for increased computing power has become a driving force behind innovation. As applications become more sophisticated and data processing requirements escalate, conventional chip design methods face unprecedented challenges. This introduction delves into the critical need for heightened computational capabilities, the delicate balance between adhering to Moore’s Law and pursuing novel architectures, and the inherent challenges embedded in traditional chip design processes.

An insatiable appetite for computing power marks the contemporary digital era. From artificial intelligence and machine learning applications to complex simulations and data analysis, the demand for enhanced processing capabilities has surged exponentially. Users, industries, and scientific endeavors constantly push the boundaries of what technology can achieve. This section provides a comprehensive overview of the pressing need for increased computing power in the face of escalating technological demands.

Balancing Moore’s Law and the Push for New Architectures

Moore’s Law, a foundational principle in the realm of technology, posits that the number of transistors on a microchip doubles approximately every two years, leading to a consistent increase in computing power. However, this Law faces challenges as the physical limitations of scaling down to 2 nanometers emerge. Simultaneously, the pursuit of new architectures becomes imperative to augment performance. This segment explores the delicate balance required to navigate the principles of Moore’s Law and the continuous push for innovative chip architectures.

Challenges in Conventional Chip Design Processes

Although practical, Traditional chip design processes are confronted with various challenges. The conventional approach involves a meticulous and time-consuming workflow, with dedicated teams of engineers working cohesively over extended periods. The intricacies of this process, coupled with the ever-growing complexity of technological requirements, create hurdles in achieving rapid advancements. This section delves into the inherent challenges of conventional chip design processes and sets the stage for exploring alternative methodologies to meet evolving technological needs.

- Innovative Approach: Researchers are exploring using ChatGPT and natural language processing to design computer chips, providing an alternative to conventional methods.

- Moore’s Law Challenge: While scaling transistor technology down to 2 nanometers aligns with Moore’s Law, new architectures and designs are essential for achieving performance improvements in chip design.

- ChatGPT in Action: ChatGPT can be prompted to design chips by specifying details like architecture and technology. Providing clear context is crucial for more accurate and complex designs.

- Limitations and Challenges: ChatGPT faces difficulty understanding and connecting hardware concepts to actual code. Training models for chip design requires bridging this gap and improving creativity in code generation.

- Google DeepMind’s Contribution: DeepMind contributes to chip implementation through circuit neural networks, optimizing circuits using reinforcement learning. Their success in chip design contests highlights the potential of these techniques.

- Documentation for Training: Using large language models to generate code documentation proves effective in training, addressing the scarcity of well-documented code for teaching models about hardware concepts.

- Circuit Optimization: DeepMind optimizes circuit synthesis using reinforcement learning, turning it into a game with a reward system. This generic improvement can be applied to various chips, including GPUs, CPUs, and AI accelerators.

- EDA Companies’ Role: Electronic design automation (EDA) companies like Synopsis and Cadence are vital in providing tools instrumental in developing modern chips by industry giants like AMD, Intel, Apple, and Nvidia.

ChatGPT in Chip Design

The groundbreaking research conducted by Georgia Tech marks a pivotal moment in the intersection of artificial intelligence and chip design. With a focus on leveraging large language models (LLMs), particularly ChatGPT, this section provides an in-depth introduction to the innovative work undertaken by researchers at Georgia Tech. By harnessing the power of natural language processing, the goal is to streamline and revolutionize the traditional chip design process.

The research at Georgia Tech aims to explore the untapped potential of ChatGPT in translating human-designed specifications into intricate chip architectures. As the introduction unfolds, it sheds light on the motivations behind using language models, the scope of their application, and the broader implications for the future of chip design.

Using Large Language Models for Chip Design

In this subsection, the focus shifts towards utilizing large language models (LLMs) as a paradigm-shifting approach to chip design. Rather than relying solely on conventional engineering methodologies, the researchers at Georgia Tech are exploring the capabilities of ChatGPT to contribute to the intricate process of designing computer chips.

ChatGPT is not merely a tool but a potential game-changer, with the ability to generate code and designs based on natural language prompts. This segment elaborates on the advantages and opportunities of integrating LLMs into the chip design workflow. It delves into the possibilities of increased efficiency, creativity, and agility in the face of ever-evolving technological demands.

Prompting ChatGPT for Specific Chip Designs

The heart of this exploration lies in the interaction between human engineers and ChatGPT. Rather than following the conventional chip design process, which involves extensive manual work and collaboration, the researchers envision a future where specific chip designs can be prompted for LLMs. This section details the methodology of instructing ChatGPT, assigning roles, and defining design parameters through natural language prompts.

Imagine a scenario where engineers can communicate their vision to ChatGPT instead of labor-intensive design processes. They can prompt the model with intricate specifications such as, “Design an AI chip based on RISC-V architecture for gesture recognition from an event camera in 7nm FinFET technology.” This subsection reveals the potential and challenges of using natural language to bridge human intent and machine-generated chip designs.

Exploring the Limitations and Challenges Faced

While employing ChatGPT in chip design is exciting, it has limitations and challenges. This segment provides a candid exploration of the hurdles researchers encounter in this groundbreaking endeavor. From ChatGPT’s lack of understanding of hardware concepts to the struggle to connect these concepts with actual code, the section paints a realistic picture of the current state of affairs.

Understanding the limitations is crucial for future advancements. As ChatGPT was not explicitly trained for chip design, the researchers at Georgia Tech are actively working to bridge the gap between natural language prompts and the intricate details of hardware architecture. This exploration of challenges sets the stage for the next steps in refining and expanding the capabilities of ChatGPT in chip design.

Bridging the Gap: Teaching ChatGPT Hardware Concepts

The integration of ChatGPT into chip design introduces challenges primarily centered around the model’s comprehension of hardware concepts. Compared to dedicated chip design tools, ChatGPT wasn’t explicitly trained for this domain during its initial training. Consequently, it needs help grasping the intricate hardware-related terminologies and concepts essential to the design process.

This section delves into the challenges researchers encounter when dealing with ChatGPT’s hardware comprehension. From struggles recognizing the nuances of transistor technology to the complexities of architectural hierarchies, the narrative provides a detailed exploration of the gaps in ChatGPT’s understanding of hardware concepts.

Connecting Hardware Concepts with Actual Code

One of the critical bridges to ineffective chip design is the seamless connection between hardware concepts and the subsequent generation of actual code. While ChatGPT demonstrates prowess in natural language processing, linking abstract hardware notions with executable lines of code poses a significant hurdle. This subsection examines the challenges and intricacies of translating high-level hardware specifications into tangible, functional code.

The narrative unfolds the complexities inherent in guiding ChatGPT to understand the theoretical aspects of chip design and articulate this understanding in the language of code. The challenges in ensuring that the generated code aligns with the intended hardware architecture become apparent, highlighting the need for a nuanced approach to teaching ChatGPT this crucial connection.

Training Models to Reason About Chip Design

Addressing the challenges in ChatGPT’s comprehension and code generation necessitates a proactive approach to training models to reason effectively about chip design. This segment outlines researchers’ strategies to enhance ChatGPT’s cognitive abilities concerning hardware design. The goal is to instill a deeper understanding of the relationships between different hardware components and their implications for the overall design.

Code Generation and Design Space Exploration

The process of integrating ChatGPT into chip design involves a sophisticated training regimen. This section provides a high-level overview of the training process, shedding light on researchers’ methodologies to enhance the model’s capabilities. The training is a pivotal phase, aiming to refine ChatGPT’s understanding of hardware concepts, ability to generate code, and aptitude for design space exploration.

Researchers guide ChatGPT through extensive datasets, exposing it to diverse scenarios encompassing a spectrum of hardware design challenges. This training is iterative and dynamic, allowing the model to continuously evolve and adapt based on the complexities inherent in chip design.

Using Differentiable Similarity for Code Comparison

A vital aspect of the training process involves utilizing differentiable similarity for code comparison. This subsection dissects the innovative approach researchers adopt to assess the quality of the generated code. Instead of relying on conventional metrics, using differentiable similarity allows for a more nuanced and context-aware evaluation.

Differentiable similarity provides a means to quantify how closely the generated code aligns with reference samples. This not only refines the training process but also introduces a feedback loop, enabling the model to learn from its iterations. The section explores the intricacies of this approach, emphasizing its role in shaping the evolution of ChatGPT’s code generation capabilities.

Challenges and Room for Improvement in Code Generation

As with any groundbreaking technology, challenges abound in integrating language models into chip design. This section delves into the specific challenges encountered during the code-generation process. From issues related to creativity in coding to the struggle to comprehend complex hardware concepts, researchers acknowledge the current limitations and outline areas for improvement.

While ChatGPT showcases remarkable capabilities, its creative and conceptual limitations become apparent when tasked with generating intricate code. The narrative discusses these challenges candidly, setting the stage for future advancements and iterative improvements in code generation methodologies.

Moving Towards Lower Stacks of the Design Process

Looking beyond the immediate horizon, researchers envision a trajectory that takes ChatGPT toward lower stacks of the design process. This involves pushing the boundaries of natural language processing to engage with more granular aspects of chip design. The narrative unfolds aspirations to move beyond high-level code generation, aiming to delve into the intricacies of design space exploration at a more fundamental level.

Progress and Outlook

In the dynamic landscape of integrating language models into chip design, evaluating progress becomes a critical aspect of gauging the viability of this innovative approach. This section delves into the meticulous process of assessing advancements, emphasizing the dual importance of data quality and quantity in shaping the evolution of ChatGPT and similar large language models (LLMs) in chip design.

Researchers recognize that the effectiveness of these models is intricately tied to the diversity and richness of the datasets used during the training process. The narrative unfolds the methodologies employed to evaluate the progress made, highlighting the significance of refining data inputs to enhance the model’s comprehension of hardware concepts and its ability to generate intricate code.

The Potential Future Role of LLMs in Chip Design

As the exploration of LLMs in chip design continues to unfold, this subsection peers into the potential future role of these language models in shaping the landscape of chip design. The narrative envisions a scenario where LLMs evolve beyond their current capabilities, becoming indispensable tools in the design process.

From generating code snippets to actively participating in design space exploration, the potential contributions of LLMs are vast. This section explores the exciting possibilities, emphasizing the potential for LLMs to bring about transformative advancements in chip design methodologies. The intersection of natural language understanding and technical intricacies promises a paradigm shift in how computer chips are conceptualized and created.

Acknowledging the Long Way to Practical Implementation

While the advancements in using LLMs for chip design are promising, it’s essential to acknowledge the considerable distance that still needs to be covered before practical implementation becomes a reality. This part of the narrative addresses the current limitations, challenges, and complexities that hinder the seamless integration of LLMs into the practical realm of chip design.

Researchers recognize that, while the potential is vast, there are hurdles to overcome. Acknowledging the long journey requires sustained efforts, iterative improvements, and a nuanced understanding of the evolving landscape. The narrative underscores the commitment to addressing challenges and refining methodologies to inch closer to the practical implementation of LLMs in chip design.

Considering the Collaboration of Machine Learning and Human Expertise

In envisioning the future trajectory, a critical aspect is the collaborative synergy between machine learning and human expertise. This section explores the delicate balance between the computational capabilities of LLMs and the nuanced understanding and creativity of human engineers in chip design.

While LLMs showcase remarkable abilities, human expertise remains an irreplaceable factor in the design process. The narrative emphasizes the need for a collaborative framework where LLMs augment human creativity, accelerate processes, and bring about efficiencies. The consideration of this collaborative approach paves the way for a harmonious integration of machine learning and human ingenuity in the ever-evolving field of chip design.

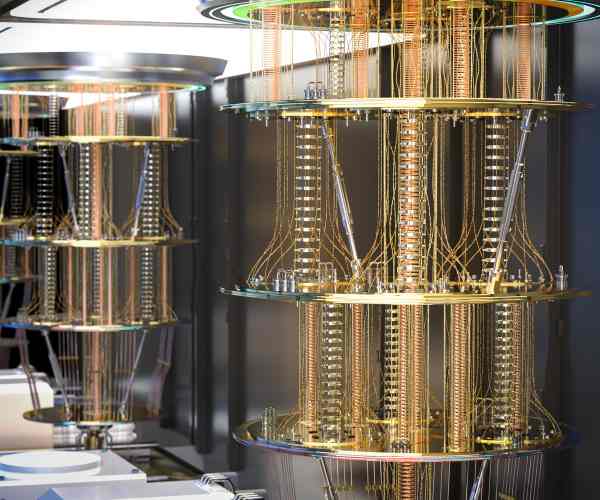

Google DeepMind’s Contribution

Google DeepMind, a pioneer in artificial intelligence, has significantly contributed to chip implementation. This section provides a comprehensive overview of DeepMind’s pivotal role in advancing the synthesis and optimization of computer chips. The narrative unfolds the multifaceted approach employed by DeepMind in reshaping the landscape of chip design, emphasizing the integration of cutting-edge AI methodologies.

DeepMind’s foray into chip implementation extends beyond conventional methods. The section delves into how DeepMind’s expertise in artificial intelligence is leveraged to address the intricate challenges of translating chip designs into physical entities. From concept to implementation, DeepMind’s role becomes a driving force in ushering in a new era of efficiency and innovation.

Introduction to Circuit Neural Networks

An essential facet of DeepMind’s contributions lies in introducing circuit neural networks. This subsection dissects the innovative approach taken by DeepMind in redefining the traditional paradigms of neural networks for chip design by transforming circuits into a neural network architecture. DeepMind pioneers a novel method for representing and optimizing complex hardware structures.

The narrative explores the intricacies of circuit neural networks, highlighting how this innovative architecture transcends the limitations of traditional neural networks. By reimagining the representation of circuits, DeepMind opens new avenues for optimization and efficiency in the design process, setting the stage for advancements in chip implementation.

Optimizing Circuits Using Reinforcement Learning

One of the distinctive features of DeepMind’s approach is the integration of reinforcement learning in optimizing circuits. This subsection unravels the methodologies employed by DeepMind in leveraging reinforcement learning techniques to enhance the efficiency and performance of circuits. The narrative delves into the principles of reinforcement learning and how it is adapted to the unique challenges posed by optimizing intricate hardware structures.

DeepMind’s utilization of reinforcement learning transforms the optimization process into a dynamic and adaptive system. By introducing a reward-based system, circuits evolve to achieve optimal configurations, ushering in a paradigm shift in how hardware structures are fine-tuned and optimized for various applications.

DeepMind’s Success in the International Chip Design Contest

DeepMind’s contributions culminate in its remarkable success in the international chip design contest. This section highlights the achievements and recognition garnered by DeepMind in the competitive landscape of chip design. By actively participating and excelling in the contest, DeepMind validates the efficacy of its methodologies and algorithms in the real-world application of designing efficient and high-performing computer chips.

The narrative explores the significance of DeepMind’s success, not just as a testament to its technical prowess but also as a beacon guiding the future of chip implementation. DeepMind’s triumph in the international arena cements its position as a trailblazer in AI-driven chip design, inspiring further exploration and innovation at the intersection of artificial intelligence and hardware engineering.

Other Players in the Field

In the realm of chip design, Electronic Design Automation (EDA) companies play a pivotal role. This section highlights two prominent players in this domain: synopsis and Cadence. These companies are integral to the technology ecosystem, providing essential tools and solutions for chip designers.

Synopsis and Cadence have made substantial contributions to the chip design industry, each bringing unique strengths to the table. This subsection explores the specific contributions of these EDA giants, ranging from advanced design tools to comprehensive solutions that streamline the chip development process. Their innovations have become indispensable for chip designers worldwide.

Both Synopsis and Cadence have been instrumental in driving advancements in electronic design, offering tools that enhance efficiency, accuracy, and overall productivity. Their contributions extend across various stages of chip development, from initial conceptualization to final implementation.

How Their Tools Have Played a Vital Role in Modern Chip Development

The tools developed by Synopsis and Cadence have played a crucial role in shaping modern chip development. This part of the narrative provides insights into the specific tools and technologies these companies have introduced, emphasizing their impact on the evolution of chip design.

EDA tools by Synopsis and Cadence have been utilized to create cutting-edge processors, GPUs, and other semiconductor devices. Their simulation, verification, and synthesis tools have become industry standards, facilitating the design of complex and high-performance chips. The section highlights the significance of these tools in achieving precision and reliability in the intricate process of chip development.

How does ChatGPT contribute to computer chip design, and what role does natural language processing play in this process?

ChatGPT is utilized in chip design by prompting it with specific instructions and scenarios. By instructing ChatGPT, users can generate designs and concepts for computer chips. Natural language processing is crucial in understanding and translating human prompts into actionable design elements. However, it’s essential to provide detailed context for more complex designs.

What challenges does ChatGPT face in chip design, and how is the research community addressing these limitations?

One significant challenge is that ChatGPT lacks a fundamental understanding of hardware concepts. The research community, exemplified by the work at Georgia Tech, is actively working to bridge this gap. The goal is to teach large language models (LLMs) to comprehend hardware concepts, connect them with code, and eventually generate meaningful and optimized chip designs.

Can ChatGPT generate code for complex chip designs, and what is the role of documentation in its training process?

ChatGPT shows promise in generating code for certain parts of chip designs, depending on complexity. However, it struggles with creativity and lacks a deep understanding of hardware concepts. Researchers use a unique approach where LLMs generate documentation based on existing code to address this. This documentation, in turn, serves as a training dataset to enhance the model’s understanding of the hardware-code relationship.

How does Google DeepMind contribute to chip implementation, and what innovative techniques are they using in circuit optimization?

Google DeepMind plays a crucial role in chip implementation by introducing circuit neural networks. These networks optimize circuits using reinforcement learning, turning the synthesis of a circuit into a game with a reward system. The agent learns to generate circuits based on performance metrics such as power, performance, and area. DeepMind’s success in an international chip design contest underscores the potential of these innovative techniques for creating efficient and high-performing chips.

Conclusion

In recapitulating the journey through integrating ChatGPT and artificial intelligence into chip design, this section revisits the immense potential of these technologies. ChatGPT, with its natural language processing capabilities and AI, has generally showcased the promise of revolutionizing chip design methodologies. The narrative underscores the transformative impact of these technological advancements’ efficiency, creativity, and adaptability.

While celebrating the strides made in incorporating AI into chip design, it is crucial to acknowledge the current limitations and areas for improvement. This subsection candidly addresses the challenges faced by ChatGPT and similar technologies, emphasizing the need for ongoing research and refinement. It recognizes that the journey toward practical implementation involves iterative improvements and a nuanced understanding of the evolving landscape.

Recognizing the Collaborative Role of Human Expertise and Machine Learning

The synthesis of human expertise and machine learning is a critical theme in the conclusion. Acknowledging that while AI contributes significantly to chip design, human ingenuity, creativity, and domain expertise remain irreplaceable. This section emphasizes the collaborative potential where the strengths of machine learning tools, like ChatGPT, complement and augment the capabilities of human designers.

In concluding the narrative, the broader impact of advancements in chip design on various industries comes into focus. The innovations discussed have far-reaching implications beyond the realm of technology. From healthcare and automotive to finance and entertainment, the ripple effects of enhanced chip design methodologies touch every sector. The section highlights how these advancements are the backbone of the technological progress that shapes our interconnected world.